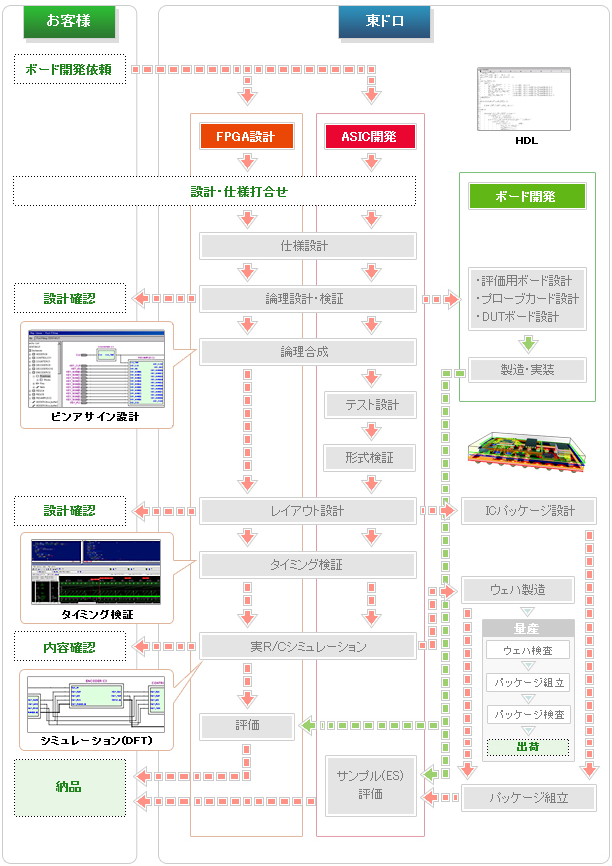

デバイス開発フロー

開発実績

画像処理

- フィルタリング

- 拡大/縮小等の画像処理

- γ/シェーディング等の補正

高速信号処理

- <25Gbps SerDes

- DDR3/DDR4-SDRAM制御

- バス制御

無線信号処理

- 無線ベースバンド信号終端

CPU組込み

- Nios

- USB/PCI

- 周辺インタフェース

使用ツール

設計・機能Simulator

【The MathWorks】

・MATLAB/Simulink

RTL Checker

【Synopsys】

・SpyGlass CDC

FPGA統合開発環境

【Intel(Altera)】

・Quartus

【Xilinx】

・ISE/Vivado

【Lattice】

・Diamond

【Microsemi(Actel)】

・Libero

論理Simulator/Debugger

【Synopsys】

・VCS

・Verdi

【Mentor】

・ModelSim